Conference 2024

**Entering the next computing paradigm: The HiPEAC Vision 2024**

Spinning out the smarts: Powering edge AI and distributed computing

Lieven Eeckhout on sustainability, Reetuparna Das on data-centric architectures and Mitsuhisa Sato on building a top supercomputer

Moving to data-centric architectures with Reetuparna Das

Mitsuhisa Sato on the road to zettascale

3 Welcome

Koen De Bosschere

- 4 News

- 16 HiPFAC voices

'By 2030, ICT could be responsible for 7-20% of all electricity demand. It's our moral duty to act'

Lieven Eeckhout

17 HiPEAC voices

'Move to data-centric architectures and leave behind computecentric designs'

Reetuparna Das

18 HiPEAC voices

'Although the progress of silicon technology is slowing, the effective use of silicon is becoming more important'

Mitsuhisa Sato

20 Technology watch

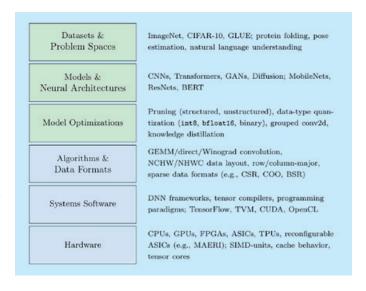

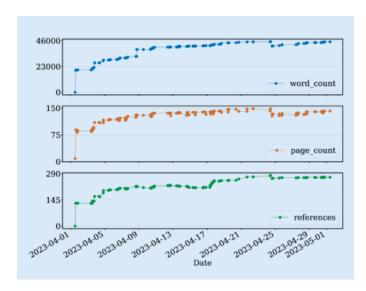

**Entering the next computing paradigm: The HiPEAC Vision 2024** *Marc Duranton and the HiPEAC Vision editorial board*

22 Distributed computing and edge AI special

Eye spy: NimbleAl's quest for a bio-inspired 3D chip for computer vision

Xabier Iturbe

24 Distributed computing and edge AI special

The VEDLIoT project: Next-generation accelerated IoT

Carola Haumann and Jens Hagemeyer

26 Distributed computing and edge AI special

Advances, challenges and applications of IoT edge computing for water-distribution networks

Domenico Garlisi, Tiziana Cattai, Redemptor Jr Laceda Taloma, Ioannis Chatzigiannakis and Francesca Cuomo

28 Distributed computing and edge AI special

How SAFEXPLAIN is working to deliver safety-critical AI

Robert Lowe

30 Distributed computing and edge AI special

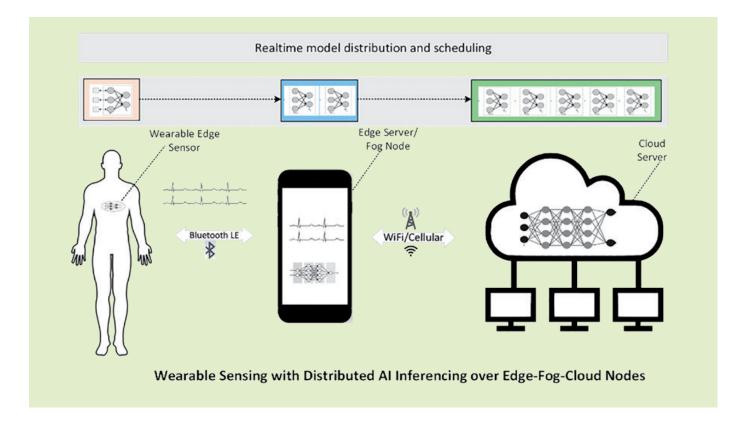

How the SWEET project is enabling robust, efficient sensing technologies for healthcare applications

Deepu John, Dimitrios S. Nikolopoulos, Bo Ji and Hans Vandierendonck

32 Distributed computing and edge AI special

Bridging horizons: Exploring the European Cloud, Edge & IoT Continuum initiative

Catarina Pereira

33 Distributed computing and edge AI special

Innovating across the edge-AI computing continuum

Ovidiu Vermesan

34 Industry focus

Frontgrade Gaisler: 'Our electronic systems and components are crucial in space-exploration missions'

Sandi Habinc and Stuart Cording

36 Innovation Europe

Self-managing systems from edge to cloud: The MLSysOps project  $\it Nikos~Bellas$

37 Innovation Europe

Breaking the edge computing status quo: The INCODE project

Clementina Piani

38 Innovation Europe

**Building the European edge AI community:**

Announcing the dAIEDGE network of excellence

José Cano and Alain Pagani

39 Innovation Europe

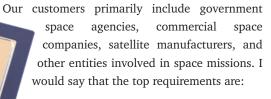

FPG-AI: ESA and the University of Pisa join forces to accelerate AI in space

Luca Fanucci

40 Innovation Europe

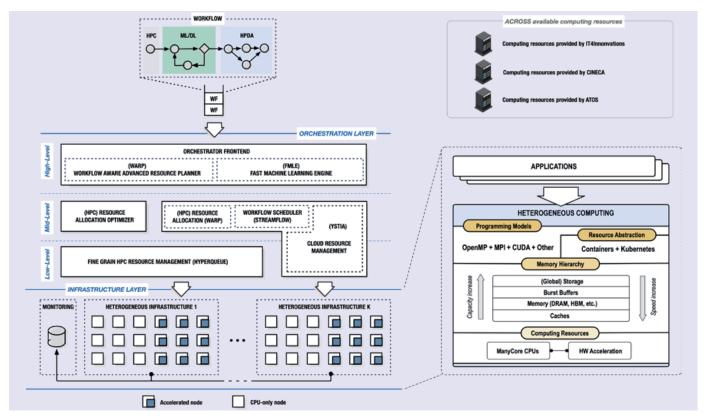

A cross-stack platform for HPC and Al workloads: The ACROSS project

Alberto Scionti

42 Peac performance

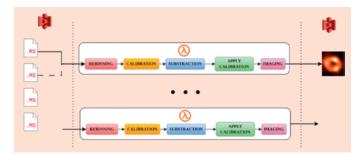

How the EXTRACT project is parallelizing data-processing pipelines

Daniel Barcelona Pons and Enrique Molina Giménez

44 HiPEAC futures

Career talk: Dominik Sisejkovic

'Innovation activities contribute significantly to students'

personal growth' - Laura Diana Cernău

Destination PhD: One researcher's doctoral journey

The DATE Young People Programme is back

Three-minute thesis: Improving the performance, portability, and productivity of hardware accelerators

Entering the next computing paradigm: The HiPEAC Vision 2024

Special feature: Edge AI and distributed computing

**Stuart Cording interviews** Frontgrade Gaisler's Sandi Habinc

Spanning the compute continuum from edge to cloud, HiPEAC (High Performance, Edge And Cloud computing) is a network of over 2,000 world-class computing systems researchers, industry representatives and students. First established in 2004. the project is now in its seventh edition. HiPEAC7 focuses on networking and roadmapping activities: bringing the computing community together in Europe, exchanging ideas, building thriving European value chains and exploring the long-term vision for computing systems.

hipeac.net 🏏 @hipeac / @hipeacjobs

in hipeac.net/linkedin hipeac.net/tv

### Funded by the European Union

The HiPEAC project has received funding from the European Union's Horizon Europe research and innovation funding programme under grant agreement number 101069836. Views and opinions expressed are however those of the author(s) only and do not necessarily reflect those of the European Union. Neither the European Union nor the granting authority can be held responsible for them.

Cover image: Panuwat on Adobe Stock

Design: www.magelaan.be Editor: Madeleine Gray

First of all, I would like to wish you a healthy and prosperous 2024 - both personally and professionally. I will remember 2023 as the year of the breakthrough of generative artificial intelligence. Almost everybody has heard about the large language model ChatGPT, and millions of people use it regularly.

Unfortunately, 2023 was also an annus horribilis: we are witnessing two horrifying and destructive wars costing tens of thousands of lives at the border of Europe: in Ukraine, and in Israel and Palestine. I hope both will come to an end in 2024.

The year 2024 will also be important at the political level. Globally, 40 countries, representing 41% of the world's population and 42% of global gross domestic product (GDP), according to calculations by Bloomberg Economics, will elect a new government. Among these, the most crucial elections are arguably the Unites States (US) presidential elections, the elections in the European Union (EU) and those in Russia. The outcome of these elections will determine the future leadership of the US, Europe and Russia, and this might lead to a different geopolitical situation in 2025, and to a safer or more dangerous world.

For HiPEAC, the year 2024 will be special too. HiPEAC1 formally started on 1 September 2004, funded by the seventh framework programme (FP7). HiPEAC has since then benefited from uninterrupted funding by the European Commission, in the early years as a network of excellence, and later as a coordination and support action. In 2024 we plan to celebrate 20 years of HiPEAC.

I am also pleased to announce that HiPEAC has been instrumental in the creation of a new project, DISCOVER-US, which aims at strengthening the research collaboration between the US and Europe in the domain of distributed computing and swarm intelligence. In the coming months, you will receive more information about events and about calls to fund EU-US collaboration.

In January 2024 we also launch the HiPEAC Vision 2024 with a new set of recommendations to tackle the many challenges of this time, ranging from the next web, artificial intelligence (AI), accelerators, cybersecurity and sustainability. I encourage you to delve into it, and get inspired by it.

Many of you will read this magazine at the HiPEAC conference, which is our flagship event. I wish you a fruitful conference, and I hope to meet you in Munich or at another HiPEAC event in 2024.

Take care

Koen De Bosschere, HiPEAC coordinator

# Willkommen in München! Welcome to Munich!

The third-largest city in Germany, and the capital of Bavaria, Munich is famous for being an engineering hub, as evidenced by the headquarters of companies such as BMW (Bayerische Motoren Werke), Siemens and Infineon. With mountain ranges including the Bavarian Alps in close proximity, and a wealth of excellent museums to visit, it's also well known for its beer, Weisswurst and Brezeln. HiPEAC caught up with HiPEAC 2024 local host Stefan Wallentowitz (Hochschule München University of Applied Sciences) to learn more about this thriving German city.

What makes Munich an ideal location for the HiPEAC conference?

Munich is one of the most thriving technology hubs of Europe. Beside the many well-known large industries it is home to many small / medium enterprises

(SMEs) and startups, along with two of the leading German universities and many research institutions. HiPEAC will therefore take place in an innovative environment, and HiPEAC will be a highlight and bring many great minds to Munich.

The quality of life is also great, which many people may even associate more with Munich. I think overall Munich is an excellent package to meet people in a great, innovative technology hub, and have great discussions over a soft drink or a famous Munich beer.

The city is famous for its architecture, including the Rathaus (city hall) on Marienplatz and the Siegestor (Victory Gate)

Munich's famous Hofbräuhaus is the venue for the HiPEAC 2024 social event

### Can you tell us about the computing ecosystem, both industrial and academic, in the local area?

The ecosystem around Munich is probably most renowned for the automotive and industrial giants that are headquartered in Munich. There are many other large enterprises here, which have a huge demand on computing specialists across all parts of the stack, and across domains.

Of course, given the presence of four large universities and a supercomputing centre, the academic ecosystem is quite thrilling. Beside the supercomputer, industrial engineering, semiconductor design and many other established fields, there are also interesting new initiatives like Munich Quantum Valley, which brings together a large representation of German industry and academia in building a hub for quantum computer expertise.

### What are some of the most interesting initiatives in HiPEAC topics at your university?

As the fourth largest university in Munich we are traditionally focused around practical education and not too much on fundamental research. But we are very strong in applied research, and I have been building a group around my strong background and involvement in RISC-V, where I am on the board of directors. We are actively involved in open-source chip design. As such, we are looking into how to build innovative chips based on RISC-V extensions and verification of those.

My other favourite topic is running WebAssembly as the virtualization technology for future embedded computing platforms. Besides support for runtime systems, programming models and fleet management, we are actively looking into hardware support of bytecode virtual machines.

### What should participants do in Munich while they're at the conference?

Munich is a beautiful city. To be honest I prefer the summer much more, because I am not into the cold. But if you bring an extra pair of socks, I would suggest that you enjoy a walk through the city, or even take the quick train ride into the mountains.

If you, like me, prefer to reduce the outside time during winter, you should definitely visit Deutsches Museum, which is a large museum centring around technology and engineering, entirely focused on impressive exhibits of historic and current devices and machines. They are remodelling and have recently re-opened a nice semiconductor exhibition, along with electronics, mathematics and encryption exhibitions. But there are many other things – including planes, optic experiments, large energy machines, robots and much more - than you can stare at and touch in a day. Feel free to get in touch with me during the HiPEAC conference to plan your stay!

### Konversationshandbuch

For your stay in Munich, here's our handy guide of key phrases, inspired by famous German thinkers (and non-thinkers).

| English                                                                        | Deutsch                                                                                                                                                     |

|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| The prudent scientist finds the most important computing innovations at HiPEAC | Die besten Innovationen in der<br>Datenverarbeitung findet der<br>gescheite Wissenschaftler auf der<br>HiPEAC (with apologies to Johann<br>Wolfgang Goethe) |

| No optimization is too small or insignificant that one shouldn't perform it    | Keine Verbesserung ist zu klein<br>oder geringfügig, als dass man<br>sie nicht durchführen sollte<br>(Theodor Adorno)                                       |

| Linux or LLVM, as long as it is an operating system                            | Linux or LLVM, hauptsache<br>Betriebssystem (inspired by<br>Andreas Möller)                                                                                 |

# **HiPEAC Technology Transfer Awards 2023 winners announced**

# And the winners are...

bit.ly/HiPEACTechTransfer23-winners

Since 2012, the HiPEAC Technology Transfer Awards have recognized examples of academic innovations examples of leading-edge technology being transferred from academia to industry. For the 2023 edition, five candidates were selected, as detailed below. The winners will be recognized in an awards ceremony at the HiPEAC conference, and first-time winners receive a cash prize of €1,000.

On behalf of HiPEAC, congratulations to the winners, who once again have shown the innovative potential of this community.

# **FPGA-Shell: Rapid Emulation of RISC-V Designs on FPGAs** Behzad Salami, Barcelona Supercomputing Center (BSC), Spain

Emulating chip designs using field-programmable gate arrays (FPGAs) is a crucial step to validate the correctness of register transfer level (RTL) design before undertaking an expensive fabrication process. With the open-source RISC-V instruction set architecture (ISA) democratizing processor

design, rapid FPGA validation is gaining even greater significance. However, FPGA emulation can itself be a bottleneck, as it requires thorough understanding of the underlying hardware and different tools and skills to processor design.

Developed by BSC during the EuroHPC project MEEP, FPGA-Shell streamlines the pre-silicon validation of RISC-V custom processors on FPGAs by automating the emulation process. FPGA-Shell automatically creates and compiles the FPGA project by connecting the RTL RISC-V design to commonly used FPGA peripherals, simply by editing a configuration file. Finally, the framework builds the project and creates the FPGA bitstream automatically, all with minimal human intervention and without the need for in-depth FPGA knowledge.

FPGA-Shell has been integrated with several open-source RISC-V systems as well as custom RISC-V designs at BSC. In collaborations with academia and industry, it is constantly evolving with new features. For example, as a part of recent agreement with Lenovo, FPGA-Shell will be supported financially and technically for the emulation of multicore RISC-V designs partitioned onto multiple FPGAs. The FPGA-Shell source code is also publicly available on GitHub for further developments.

- ☑ github.com/MEEPproject/fpga\_shell

- meep-project.eu

# Enhancing Pavlovian-training experiments with GPU-accelerated machine learning

Christos Strydis, Erasmus Medical Center, Netherlands

In neuroscience, Pavlovian eyeblink conditioning is a crucial experiment for assessing human learning processes. Traditionally, researchers have tracked eyelid movements using potentiometers or electromyography. Recently, computer vision and image processing have offered alternatives,

but these require human involvement and lack real-time capabilities. To address this, the neurocomputing laboratory of the neuroscience department at Erasmus Medical Center in Rotterdam joined forces with the startup Blinklab, which turns mobile phones into devices for conducting neurobehavioural evaluations. Researchers evaluated face-and landmark-detection algorithms for automated eyelid tracking, a technique which could help enable closed-loop experiments with promise for insights into neurological disorders.

After evaluating various detection algorithms, histogram of oriented gradients (HOG) and ensemble of regression trees (ERT) algorithms were chosen for eyelid detection and accelerated on graphics processing

units (GPUs) and central processing units (CPUs), yielding substantial speed improvements. The algorithm achieved an application runtime of 0.533 milliseconds per frame, surpassing real-time requirements for human eyeblink conditioning.

### ORBIK Cybersecurity: A cybersecurity spinoff for equipment manufacturers

Salvador Trujillo, ORBIK Cybersecurity, Spain

As embedded systems become increasingly interconnected, they are also increasingly susceptible to vulnerabilities. In addition, they are increasingly subject to regulatory requirements, such as the European Union's Cyber Resilience Act, as well as needing to meet customer requirements. Over the

last few years, IKERLAN has developed a range of technological assets aimed at enhancing the cybersecurity of equipment manufacturers, with a particular emphasis on those incorporating industrial control systems with dedicated embedded electronics.

Drawing on IKERLAN's expertise and resources, the ORBIK Cybersecurity spinoff was created to provide cybersecurity-assessment services and help clients meet industry standards, such as IEC62443. The fledgling company is already working with clients including in the energy sector, such as equipment providers for power grids.

Find out more about ORBIK Cybersecurity in this video:

☑ vimeo.com/883948062/778891f902

### Empowering next-generation processor design: EDA tools for faster time-to-market

Lennart M. Reimann, Niko Zurstraßen, Jose Cubero, Lorenzo Pfeifer, Jan Moritz Joseph – all RWTH Aachen, Germany

In recent years, processor complexity has been growing exponentially, and design tools have been unable to keep pace. Current electronic design automation (EDA) tools are often unable to fully leverage higher core counts in contemporary processors, thus achieving only marginal performance gains, while having to cope with larger, increasingly complicated designs.

Left to right: Niko Zurstraßen, Jose Cubero, Lorenzo Pfeifer and Lennart Reimann

In this technology transfer, the team at RWTH Aachen developed two design tools and transferred these to a major international information and communication (ICT) company as part of joint research projects. The first, a tool for rapid prototyping using abstract modelling of the target hardware, allows users to understand application requirements and derive an initial architecture. The second, a parallel simulation kernel for the open-source project gem5, enables microarchitecture optimization and provides an understanding of the system-level performance impact of low-level design decisions. These tools are being deployed at scale for the company's next generation of processors.

### **BiodAlverse: Smart conservation technologies** Jorge Fernandez-Berni, Institute of Microelectronics of Seville (CSIC-Universidad de Sevilla), Spain

Quite apart from the incalculable loss to the planet, the sixth mass extinction which is currently ongoing also constitutes a critical threat to the future of human civilization due to the associated degradation of ecosystem services. Technology can play a role in helping to bend the curve of

mass extinctions by keeping a record of the state of species and ecosystems, identifying causes of extinction and degradation, assessing the effectiveness of mitigation measures, and monitoring the evolution of the environment while collecting data to drive future actions and make informed decisions.

The spinoff BiodAlverse came about from many years of interdisciplinary research on conservation technologies jointly conducted by two groups at the Institute of Microelectronics of Seville and Doñana Biological Station in Andalusia, Spain. Leveraging researchers' extensive know-how in embedded artificial intelligence (AI) and internet-of-things (IoT) systems, as well as in the application of technology to conservation, BiodAlverse provides a scalable, end-to-end technological infrastructure for effective wildlife monitoring, ranging from real-time reporting to long-term habitat assessment.

The key technologies at the core of BiodAlverse's value proposition are:

- 1. a modular, multi-sensor, low-cost, low-power, IoT platform that can be easily adapted to different customer requirements;

- 2. Al algorithms tailored for efficient execution on embedded systems; and

- 3. a cloud platform that collects data coming from systems deployed in the field and aggregates them for proper visualization and analysis through customized panels and notifications.

Further information on BiodAlverse may be found in the 'SME snapshot' article in HiPEACinfo 69 (July 2023).

Have you successfully transformed a research project into industryready results? Find out more about the HiPEAC Technology Transfer Awards on the HiPEAC website hipeac.net/awards/#/tech-transfer

# SiPearl to equip JUPITER, Europe's first exascale machine

In October, the European semiconductor company SiPearl announced a contract to equip JUPITER, the first European exascale supercomputer. JUPITER's general-purpose cluster module will be based on SiPearl's first-generation microprocessor, Rhea1.

According to SiPearl, this first contract is a major milestone for the company in fulfilling its mission assigned by the European Union through the European Processor Initiative (EPI) consortium: to ensure European sovereignty with the return of high-performance, low-power microprocessor technologies in Europe.

Owned by the EuroHPC Joint Undertaking, JUPITER will be installed at the Forschungszentrum Jülich campus in North Rhine-Westphalia and built by a consortium composed of Eviden (the Atos Group business leading in advanced computing) and ParTec (the German modular supercomputing company). The expected budget is €273m.

☑ bit.ly/SiPearl\_JUPITER\_2023

"A major milestone in SiPearl's mission to ensure European sovereignty"

# **BSC's AccelCom group** announces ODOS offloading support for NVIDIA DOCA

Antonio J. Peña and Sergio Iserte, BSC

The AccelCom group at Barcelona Supercomputing Center (BSC), led by HiPEAC member Antonio J. Peña, has developed a solution named ODOS (OpenMP offloading support for NVIDIA DOCA) that provides support for standard OpenMP offloading and semantics for data processing units (DPUs).

A programmable system-on-chip, DPUs are used to accelerate the most demanding workloads. They combine industry-standard, software-programmable processing elements, such as central processing units (CPUs) and graphics processing units (GPU), with networking and other SoC components.

ODOS extends the LLVM compiler infrastructure to enable OpenMP offloading for NVIDIA BlueField DPUs. It allows users to offload computations to GPUs and / or DPUs using the widely adopted OpenMP syntax. This removes barriers for new users, allowing them to leverage the power of DPUs within their existing programming frameworks.

NVIDIA provides assistance and resources for ODOS, funding its development and facilitating its promotion among the user community.

Antonio J. Peña said: 'I expect to soon see many more applications benefiting from the performance advantage of NVIDIA BlueField DPUs thanks to the seamless interface provided by ODOS. We are already collaborating with NVIDIA on new functionalities and enhanced performance.'

'By integrating DPUs seamlessly into the OpenMP ecosystem, we are empowering programmers with greater access to accelerated computing, unlocking new possibilities for high-performance applications,' said Gilad Shainer, senior vice president of networking at NVIDIA.

# **DISCOVER-US** initiates new era in EU-US distributed computing and swarm intelligence research

Launched on 1 January 2024, the DISCOVER-US project is a 30-month project that is set to energize pre-competitive collaborative research between the European Union (EU) and United States (US) National Science Foundation around the computing continuum, distributed computing, and swarm intelligence.

A Horizon Europe coordination and support action, the project will mutually reinforce the research capacity of the EU and US in this area, ultimately contributing to a stronger collaborative transatlantic research infrastructure and strengthening Europe's position in cloudto-edge computing, the internet of things (IoT) and the tactile internet. This will be achieved by integrating relevant elements of computing, connectivity, IoT, artificial intelligence (AI) and cybersecurity.

'The name DISCOVER-US has two meanings: researchers from the US will discover "us" in Europe, while EU researchers will discover research in the US,' says project coordinator Koen De Bosschere (Ghent University). 'The project will enhance synergies, experience and knowledge sharing, building an EU-US collaborative research ecosystem for pre-competitive research in topics related to the computing continuum, distributed computing and swarm intelligence.'

The project offers an excellent opportunity for HiPEAC members working on research for the computing continuum, distributed computing, and / or swarm intelligence to build partnerships with their counterparts in the US and work on mutual research projects.

DISCOVER-US especially seeks research contributions that:

- Allow the level of abstraction to be raised in the modelling, development, execution and orchestration of complex applications deployed on the computing continuum, especially near and towards the edge.

- Generate new concepts for distributed computing, the computing continuum, swarm intelligence and edge intelligence.

- Allow trustworthy AI-enabled self-organized, dynamic and adaptive management of the resources required for execution near and towards the edge of the compute continuum.

- Deliver collaborative programming frameworks and software development tools.

- · Help improve human understanding and control of those complex applications.

Around 20 pre-competitive EU-US research collaborations will be funded, and a Dagstuhl-style workshop will be held to work on key areas. The project aims to result in a transatlantic research community of around 100 senior researchers, and to develop a research vision on the main topics.

The steering board comprises the following HiPEAC members:

- Coordinator Koen De Bosschere, leader of the Computer Systems Lab at Ghent University and coordinator of HiPEAC;

- Rosa M. Badia, manager of the Workflows and Distributed Computing Group at Barcelona Supercomputing Center (BSC);

- Marc Duranton, member of the Research and Technology Department of CEA (French Atomic Energy Commission) and editor in chief of the HiPEAC Vision;

- Tullio Vardanega, associate professor in the Department of Mathematics, University of Padova; and

- Ovidiu Vermesan, chief scientist at SINTEF.

### **FURTHER INFORMATION:**

discover-us.eu

DISCOVER-US has received funding from the European Union's Horizon Europe research and innovation programme under grant agreement number 101135064. Views and opinions expressed are however those of the author(s) only and do not necessarily reflect those of the European Union. Neither the European Union nor the granting authority can be held responsible for them.

# New era for Czech science as EOSC initiative launches in the Czech Republic

Marie Hostalkova, Masaryk University

The European Open Science Cloud (EOSC) initiative aims to connect scientific communities, establish a robust data-storage and sharing system, and enhance access to research data for scientists and organizations. The Ministry of Education, Youth and Sports (MEYS) of the Czech Republic officially declared support for the initiative on 4 September 2023, signalling a pivotal moment in EOSC's implementation at the national level.

Managed by Masaryk University in collaboration with CESNET and IT4Innovations at VSB — Technical University of Ostrava, the strategic project EOSC-CZ operates under the Jan Amos Comenius Programme, financially supported by the MEYS to advance the scientific environment in the Czech Republic. Alongside the Czech Academic and Research Discovery Service (IPs CARDS) project of the Czech National Technical Library of Technology, EOSC-CZ plays a crucial role in establishing a unified environment for managing and searching for scientific information resources.

With an allocated budget of 450 million CZK over six years, the MEYS of the Czech Republic emphasizes the transformative nature of EOSC-CZ, going beyond infrastructure investments to fundamentally change the system of scientific work.

The recent legal approval marks a critical milestone, allowing the EOSC-CZ project to fully engage in its activities and offer services to the Czech scientific community. This transformative initiative is ready to inaugurate a new era of collaborative and easily accessible scientific research in the Czech Republic.

# Czech Republic one step closer to quantum computer

Branislav Jansik, IT4Innovations

The international LUMI-Q consortium has signed the hosting agreement in Luxembourg for the acquisition and operation of a quantum computer. It will be installed at IT4Innovations National Supercomputing Center in Ostrava, Czechia, in 2024 and become the first Czech quantum computer, which will also be available to the European research community.

The LUMI-Q consortium, which brings together nine European countries: Belgium, Czechia, Denmark, Finland, Germany, the Netherlands, Norway, Poland, and Sweden, aims to provide academic and industrial users with a quantum computer based on superconducting qubits with a star-shaped topology. Its advantage is that it minimizes the number of so-called swap operations and enables the execution of very complex quantum algorithms. The assumption is that it will contain at least 12 qubits. This quantum computer will be directly connected to the EuroHPC supercomputer KAROLINA, located at IT4Innovations in Ostrava. In addition, the plan is to connect it to other EuroHPC supercomputers, especially those hosted by other members of the LUMI-Q consortium, such as the most powerful European supercomputer LUMI, in Finland, or the Helios supercomputer, which will be located in Krakow, Poland.

'Signing the agreement to host the LUMI-Q quantum computer in the Czech Republic is an important milestone not only for the Czech research community in the field of quantum computers and algorithms but also represents a significant step towards developing European quantum computing resources. Together with other European partners, we are creating an important element of future scientific progress in quantum computing and its applications,' said Vit Vondrak, Managing Director of IT4Innovations.

'We expect that not only the Czech scientific community will gain access to our quantum computer through e-INFRA CZ, but also all consortium members. As 50% of the cost of the LUMI-Q quantum computer is covered by EuroHPC JU, users from all over Europe will also have access to it. Finally, our goal is to make quantum computing available to industrial companies,' says Branislav Jansik, Supercomputing Services Director at IT4Innovations and the LUMI-Q consortium Coordinator.

# Italian project RETICULATE tackles real-time, secure AI for CPS

Alessandro Biondi (Scuola Superiore Sant'Anna Pisa) and Alessandro Cilardo (University of Naples Federico II)

Next-generation cyber-physical systems (CPS), are increasingly reliant on artificial intelligence (AI), particularly deep neural networks (DNNs). In CPS, DNNs must (i) execute under real-time constraints, (ii) ensure energy efficiency, as required by most embedded devices, and (iii) ensure confidentiality and integrity of design and user data. DNNs usually need hardware acceleration, for example system-on-chip (SoC) platforms augmented with field-programmable gate array (FPGA) fabrics.

A project supported by the Italian PRIN research funding program, RETICULATE (REal-Time and seCUre acceleration framework for Artificial inTElligence) will address the technical challenges for the adoption of AI in future CPS, by delivering an innovative DNN framework for FPGA-based SoCs offering advanced capabilities in terms of real-time performance and cybersecurity. RETICULATE is led by Scuola Superiore Sant'Anna Pisa (principal investigator (PI): Alessandro Biondi), with the University of Naples Federico II as a partner (local PI: Alessandro Cilardo).

The project will develop problem-specific timing analysis methods to predict the performance of DNN accelerators and enable design space exploration, taking into account time predictability. As DNN accelerators are memory intensive, the project also aims at exploring memory-driven optimizations in FPGA platforms. Furthermore, since existing acceleration platforms do not provide any built-in security features, RETICULATE will develop specific mechanisms at the architecture level to increase the security of the CPS as a compute platform. Cybersecurity threats will also be considered at the level of AI algorithms, by providing DNN accelerators with efficient mechanisms detecting adversarial attacks and unsafe inputs in general.

The framework delivered by RETICULATE will be tested and demonstrated in the context of autonomous navigation with real-time Al-based perception for a robotic land rover as well as for confidential remote inference in a smart health application.

# **IT4Innovations** scientists working on **ESA project AIOPEN**

Barbora Polakova, IT4Innovations

Funded by the European Space Agency (ESA), AIOPEN aims to create a user-friendly, intuitive platform that allows users, regardless of their technical expertise, to use and apply artificial intelligence to process remote sensing and satellite imagery data. The project, which involves IT4Innovations, Space Applications Services, Telespazio, KP Labs, and SERCO, will provide visual workflows and pre-built templates that users can customize with available Earth observation data.

The AIOPEN platform will be created by combining and extending the ASB, EOPEN, and EOEPCA platforms with new, innovative services based on artificial intelligence and machine learning. Two case studies will be implemented on the platform during the project.

The Urban Change Detection case study, for which IT4Innovations is responsible, aims to use machine learning models to monitor urban growth, thereby enabling comprehensive regional development planning and preventing unwanted urban sprawl. Earth observation data and deep neural networks will be used to detect urban change, and a digital twin of Earth's (urban) changes will also be created. Artificial intelligence will allow satellite imagery to be analysed in depth.

Another long-standing problem in many countries is deforestation, which the AIOPEN team will also address under the leadership of KP Labs. Monitoring, segmentation, and analysis of forests will also be carried out using artificial intelligence, algorithms, and publicly available data.

Vaclav Svaton, project investigator for IT4Innovations, commented: 'The AIOPEN project aims to extend existing commercial platforms with AI functionalities. The project's results, i.e. the provision of services enriched with innovative AI functionalities, will be published in the project's network of resources.'

☑ eo4society.esa.int/projects/aiopen

# **Building the biodiversity** component of the Digital Twin of the Ocean

Fabiana De Carlo, Trust-IT Services

Marine habitats present specific issues when it comes to observing, mapping, and monitoring biodiversity. While significant advancement has been made in Europe to collect, harmonize, and make available data on marine biodiversity, a large portion of the data collected is currently inaccessible; this is referred to as 'sleeping data'.

The DTO-BioFlow project's primary objective is to awaken sleeping biodiversity data, enabling smooth integration of existing and new data into the European Digital Twin of the Ocean (EU DTO).

Over the next four years, the DTO-Bioflow consortium will work on consolidating standards, quality control, communication protocols, harmonization pipelines, data products, data models, ingestion procedures and incentives for sustainable connection to improve the interoperability and digitization of biodiversity data. The project will also test out various technologies to carry out species monitoring on a massive scale. The end-to-end approach will be demonstrated via science-based use cases and via mechanisms to monitor, measure progress and drive community action towards increasing biodiversity data flows.

DTO-BioFlow kicked off on 27 September in Ostend, Belgium. The consortium, led by the Flanders Marine Institute, comprises 30 partners from 14 countries, including research centres, infrastructure hosts, networks, associations, global aggregators, platforms, and others.

### FURTHER INFORMATION:

dto-bioflow.eu

# **EXA4MIND** extreme data platform presented at EBDVF 2023

Jan Martinovic, IT4Innovations

Organized by the Big Data Value Association, the European Big Data Value Forum (EBDVF) took place in Valencia on 25-27 October. The EXA4MIND project presented its activity in developing an extreme data platform for advanced data analysis and knowledge extraction integrated with European supercomputing and data spaces at this event.

EBDVF serves as a platform for the exchange of knowledge and the exploration of novel perspectives on big data and AI to industry experts, developers, researchers, and policymakers. The three-day event featured 250 speakers who presented topics related to big data and artificial intelligence over a series of plenary and special sessions, workshops and panel discussions.

The EXA4MIND was represented by its team and management, showing its commitment to the European big data community. The project co-sponsored EBDVF 2023 and had a booth in the exhibition.

'The forum gave me very valuable insights into the landscape of European data spaces and big data. Besides presenting the project, we got key tips on, for example, the Dataspace Protocol from the Data Spaces Support Centre and the International Data Spaces Association, enabling us to make connections,' said Stephan Hachinger (Leibniz Supercomputing Centre), EXA4MIND science and co-design coordinator.

EBDVF 2023 attracted 650 attendees; its next edition will take place in Budapest.

**FURTHER INFORMATION:**

deuropean-big-data-value-forum.eu

# **Industry 4.0 conference returns** to Bosnia and Herzegovina

Isak Karabegović, Academy of Sciences and Arts of Bosnia and Herzegovina

On 5-6 October 2023, the Academy of Sciences and Arts of Bosnia and Herzegovina (ANU BiH) organized a conference named 'Basic technologies and models for the implementation of Industry 4.0' in Sarajevo. The conference was organized in collaboration with the Society for Robotics of Bosnia and Herzegovina, the Foreign Trade

Chamber of Bosnia and Herzegovina, and the Chamber of the Economy of the Federation of Bosnia and Herzegovina.

The aim of the conference was to share knowledge about developing and implementing technologies in industry 4.0, and to adapt to the challenges while taking advantage of the opportunities this new paradigm offers.

Industry 4.0 brings a change of business paradigms and production models that will be reflected at all levels of production processes and supply chains. These changes are caused by technological advances such as robotics and automation, the internet of things (IoT), big data, 3D printing, smart sensors, radio frequency identification (RFID), virtual and augmented reality, artificial intelligence, advanced security systems, etc.

Benefits of the industry 4.0 approach include improved product quality, reduced working hours, enhanced safety, minimized costs, and ongoing maintenance. However, there are many challenges to the implementation of industry 4.0, such as changing business bias, resource planning, legal issues, security issues, and standardization.

While many small / medium enterprises (SMEs) in the Western Balkans intend to gradually introduce smart solutions, methods and technologies, the costs of implementation and high complexity of the technologies present major challenges. It is therefore necessary to create a framework that describes the key issues and emphasizes possible answers, while also providing a platform for private-public cooperation and partnership on emerging issues.

In this context, and building on previous events such as the industry 4.0 workshop organized in October 2022, as reported in HiPEACinfo 68, this conference brought together experts from all over the country. Topics included edge AI, the role of software engineering in industry 4.0, engineering skills for intelligent manufacturing, advanced robotics, and digital twins.

Conference proceedings are available for download from the ANU BiH digital library https://bit.ly/BiH\_Industry-4-0\_Oct23\_proceedings

# **Next-generation** solutions for sexual health with bitsxlamarató

Organized by the Facultat d'Informàtica de Barcelona (FIB) at the Universitat Politècnica Catalunya-Barcelona Tech Hackers@UPC, Barcelona Supercomputing Center and the Institut de Recera Sant Pau, bitsxlamarató is an annual hackathon which contributes to the 'Marató' fundraising initiative of Catalan broadcaster TV3. Bringing together programmers, academics and health professionals, the hackathon seeks to find technology solutions for healthcare.

The 2023 edition, which took place in Barcelona on 16-18 December, focused on sexual and reproductive health. In total, 150 people took part, including 125 hackathon participants, mentors and organizers. There were a total of 35 projects split among four different challenges, covering different aspects of sexual and reproductive health. For the participating health organizations, the hackathon provided solutions which will help them continue their vital work.

As in previous years, HiPEAC supported the hackathon, providing welcome packs and setting up a HiPEAC Jobs wall.

fib.upc.edu/ca/la-marato

# Antonio J. Peña receives Agustín de Betancourt award

On 21 November 2023, HiPEAC member Antonio J. Peña (Barcelona Supercomputing Center) was awarded the Agustín de Betancourt y Molina Prize for young researchers by the Spanish Real Academia de Ingeniería. The award recognizes professionals who have made original and relevant contributions in engineering, specifically valuing aspects related to technology transfer.

The jury noted the impact of technology transfer of Antonio's research, with contributions to the MPICH implementation of the message passing standard 'MPI', whose derivatives are used in the largest supercomputers in the world, thus contributing to much of the progress in the fields of computational science. They also valued his collaborations with Intel and NVIDIA in software research and development (R+D) for the democratization of the use of heterogeneous resources in supercomputing, such as different accelerators and memory subsystems.

On behalf of HiPEAC, congratulations to Antonio!

# **ACACES 2023 and HiPEAC** 2024 on HiPEAC TV

Videos of lectures from ACACES 2023 are now available on the HiPEAC YouTube channel, HiPEAC TV. You'll also find interviews, keynote talks, social media shorts, animations, and more.

More HiPEAC 2024 videos will be available in due course - stav tuned for further information.

☑ hipeac.net/tv

# Aida Todri-Sanial awarded AiNed fellowship grant

HiPEAC member Aida Todri-Sanial (Eindhoven University of Technology - TU/e) has been awarded an AiNed Fellowship Grant for her research project 'AI-on-ONN: Online Learning for Sense-to-Compute Edge AI with Oscillatory Neural Networks'. This project will investigate energy-efficient computing and processing of signals from the ever-growing number of sensors in smart systems, estimated to reach 45 trillion by 2030.

Aida's research focuses on a novel computing paradigm whereby programs (functions) are directly mapped onto the computational hardware, based on the principle 'let physics do the computing'. The problem she will address in this fellowship is to investigate whether oscillatory neural networks (ONN) can allow a seamless sense-tocompute paradigm.

AiNed Fellowship Grants help Dutch academic knowledge institutions to attract talented researchers in artificial intelligence (AI). Awarded by the Dutch National Growth Fund programme, they aim to consolidate the AI knowledge and education base in the Netherlands and strengthen the national AI ecosystem.

'Over the last few years, I have been working with my team and international collaborators on developing ONN computing covering aspects from computing models, algorithms and its physical implementation in hardware. This fellowship is a great boost to allow to develop this novel sense-to-compute paradigm with ONNs and assess its pros and cons in edge Al,' Aida commented.

Congratulations on behalf of HiPEAC!

☑ bit.ly/AiNed\_Aida-Todri\_Sanial

# **ETH Zurich students scoop** multiple awards at SC23

A team of students from ETH Zurich, going by the name of RACKlette, have become the first European winners of the Student Cluster Competition at the annual Supercomputing conference, SC23, which was held in Denver, Colorado, United States, in November 2023.

The Student Cluster Competition at Supercomputing was started in 2007 with the aim of introducing the next generation of students to the high-performance computing (HPC) community, bringing together undergraduate teams from around the world. Sponsored by various hardware and software vendors, each team is tasked with designing, building, and operating a small computer cluster.

For the 2023 edition, 11 teams took part, including six from the United States, three from China, one from Singapore and one from Switzerland.

The RACKlette team was supervised by HiPEAC member Torsten Hoefler (ETH Zurich / Swiss National Supercomputing Centre-CSCS), with significant contributions from Hussein Harake, a senior systems engineer at CSCS. The team was sponsored by E4 Computer Engineering, NVIDIA, SPCL at ETH Zurich, HaslerStiftung, and CSCS.

In related news, Marcin Chrapek, Mikhail Khalilov and Torsten Hoefler won the SC23 Best Student Paper and the Best Reproducibility Advancement Award for their paper 'HEAR: Homomorphically Encrypted Allreduce'.

Congratulations on behalf of HiPEAC!

Top: Team RACKlette at SC23; Bottom: Marcin Chrapek accepting the Best Student Paper Award, with Torsten Hoefler

# **Dates for your diary**

### **HiPEAC** webinars

Check the HiPEAC website to keep up to date on forthcoming dates ☑ hipeac.net/webinars

### ARITH 2024: 31st IEEE International Symposium on Computer Arithmetic

10-12 June 2024, Málaga, Spain

**☑** arith2024.arithsymposium.org

### DATE 2024: Design, Automation and Test in Europe

25-27 March 2024, Valencia, Spain

HiPEAC Jobs activities with the Young People Programme

☑ date-conference.com

### **EuroSys 2024: European Conference on Computer Systems** 20-24 April 2024, Athens, Greece

Includes MECC 2024: MetaOS for the Cloud-Edge-IoT Continuum (22 April) / Workshop by FLUIDOS, aerOS, ICOS, NebulOuS, NEMO, and NEPHELE

☑ meccworkshop.github.io

### GraphSys'24: 2nd Workshop on Serverless, Extreme-Scale, and Sustainable Graph Processing Systems

Co-located with ICPE 2024

7-8 May 2024, London, UK

Paper submission: 22 January 2024

☑ sites.google.com/view/graphsys24

### HPDC 2024: 33rd ACM International Symposium on High-Performance Parallel and Distributed Computing

Abstract submission: 18 January 2024

hpdc.org/2024

### Euro-Par 2024: 30th International European Conference on **Parallel and Distributed Computing**

Abstract submission: 5 March 2024

### **ISC High Performance**

12-16 May 2024, Hamburg, Germany

☑ isc-hpc.com

### HEART 2024: 14th International Symposium on Highly-Efficient Accelerators and Reconfigurable Technologies

19-21 June 2024, Porto, Portugal Submission deadline: 18 March 2024

fe.up.pt/heart2024

HiPEAC 2024 keynote speaker Lieven Eeckhout (Ghent University) is an ACM and IEEE Fellow, and the recipient of multiple awards including the Maurice Wilkes Award, OOPSLA Most Influential Paper Award, and MICRO and ISPASS Best Paper Awards, as well as five European Research Council (ERC) grants. HiPEAC caught up with Lieven to learn about his background in computer architecture and his recent focus on sustainability.

# 'By 2030, ICT could be responsible for 7-20% of all electricity demand. It's our moral duty to act'

### How did you end up specializing in your field?

I started studying engineering because I loved math. In my first year at the university, during a course on numerical techniques where we had to program optimization problems, I realized that I loved programming and I found it fascinating that I could experiment at home behind a computer. Over time, I realized that I was most interested in how computer systems work, how to design them and how to program them. During my PhD I became particularly interested in performance modelling and workload characterization. Later, I also got interested in microarchitecture and computer-system resource management. My latest focus in on sustainability.

What prompted you to start researching sustainability? Why should it be on the HiPEAC community's radar?

I've always loved nature. Watching how humanity is exhausting the planet, and witnessing young people protesting for climate change, I started wondering how big the impact of information and communication technology (ICT) on the environment was. I proposed to my department that we should start a new course on sustainable computing, and they approved. It was while I was working on the course material that I became really interested in the topic. At the time, two to three years ago, there was no course

material available elsewhere, and so I had to compose my lecture material myself. I did a lot of research trying to make sense of the limited, disparate data that is available.

I believe the HiPEAC community should indeed focus on sustainability. ICT today is responsible for 2-4% of greenhouse gas emissions. This is on par with the aviation industry, and it is growing. Some projections state that by 2030, ICT will be responsible for 7-20% of all electricity demand. We should do something. I would even state that it's our moral duty to act! And I believe there is lots we can do, as hardware designers, system integrators, and software developers.

What, for you, are the main issues concerning sustainability?

It turns out that when looking at the total environmental footprint of a computing device, the embodied emissions - the emissions for manufacturing, assembly, transportation, and end-of-life processing – are dominant compared to the operational emissions during a device's lifetime. This is the case for personal mobile devices such as smartwatches, smartphones, tables, laptops as well as for servers in hyperscale data centres. Operational emissions seem to dominate for always-connected devices.

My own analyses indicate that embodied emissions will soon dominate for nearly all computing devices. The reason is twofold. On the one hand, devices are becoming increasingly energy efficient, so this reduces the operational footprint. On the other hand, the demand for computer chips continues to increase - by around 9% per year - and, in addition, semiconductor manufacturing is becoming increasingly energy demanding - an increase of around 11% per year. Hence we can expect that the embodied footprint will continue to increase.

As computer engineers and scientists, we therefore need to start designing computer systems with sustainability and especially the embodied footprint as a primary design goal. We need to start designing smaller chips to reduce the embodied carbon

Cartoon by Arnout Fierens from the HiPEAC Vision 2024

footprint. To pick one example: dark silicon - or providing tens of accelerators on chip that are powered on only when needed – is considered the way forward to continue scaling performance as progress in chip technology is slowing down, but it is harmful for sustainability. The reduction in operational footprint is unlikely to outweigh the embodied footprint that these accelerators incur. Sustainability requires us all as a community to start thinking differently about how to design computer systems. We need to design computer systems more holistically considering the overall environmental footprint.

### What are the main challenges in researching and teaching this topic?

A major challenge is that there is little data available pertaining to sustainability, and when data is available, there is quite a bit of uncertainty about the data. Companies are starting to publish lifecycle assessment reports about the products they bring to market, and these reports also acknowledge that some numbers are based on industry averages or estimates.

My take on it is that we should embrace the uncertainty and go back to first principles using proxies for the embodied and operational footprint. We can use chip area as a proxy for the embodied footprint and energy / power as a proxy for the operational footprint. Reasoning about chip area and energy / power and performance in a holistic manner enables computer engineers and scientists to make reasonable design decisions despite the uncertainty. So, while we should continue to aim for high-quality data and better understand the environmental footprint of computing, there is no time to waste, and I believe we can make a difference today.

Teaching sustainability topics is challenging but very rewarding and interesting. Sustainability is a fundamentally multidimensional problem, and there are so many stakeholders. Sustainability is also a much broader problem than global warming and carbon emissions: it covers raw material extraction, end-oflife repurposing or recycling, water consumption, business models, legislation, etc. This oftentimes leads to very interesting discussions in class where we analyse the pros and cons of sustainable developments.

For example, while we as engineers and scientists can try to design computing devices with a lower carbon footprint and less material use, there is always the risk of a rebound effect, also called Jevons' paradox. It is well known that making devices more efficient oftentimes leads to increased usage and deployment. Given our linear economy, which is based on selling stuff, I believe that we need new business models towards a circular economy. Also, we need regulation and legislation to temper the demand for new devices and the increase in the environmental footprint of ICT.

### What are your career highlights and future plans?

My whole career has been a highlight in my view. It was great to grow as a researcher during my PhD and postdoc period, and later as a professor. Mentoring students, seeing how they learn new stuff in class, seeing how they grow as researchers is all very rewarding. I always enjoy working on a new project with collaborators and students. In the beginning there are lots of unknowns and you don't really understand what the problem is and how to tackle it. But over time you start understanding what's going on, and the most wonderful moment is when all pieces of the puzzle come together.

Of course, it's also very rewarding to be able to publish your research in the field's top-tier conferences and then also receive international recognition through awards - I've been lucky enough to receive a few. As for the foreseeable future, I'm planning to focus my research on making our computer systems more sustainable.

HiPEAC keynote speaker Reetuparna Das is an associate professor at the University of Michigan. She has previously worked at Intel Labs and the Center for Future Architectures Research, and has co-founded a precision-medicine start-up, Sequal Inc.

# 'Move to data-centric architectures and leave behind compute-centric designs'

### How did you get into computer architecture research?

Discovering computer science in middle school ignited my love for programming. Growing up, my curiosity about how computers work deepened, focusing on their 'brain' - the processors. Taking an undergraduate computer architecture class intensified this interest; I was particularly fascinated by concepts like speculation, prediction, and caching. This experience confirmed my decision to pursue a PhD in computer architecture, and I have not looked back since.

### What are the most pressing research topics in the field?

The global datasphere is experiencing unprecedented growth, with the data generated in the next five years expected to surpass the cumulative amount created since the inception of digital storage. Propelled by advanced technologies like artificial intelligence (AI), the internet of things (IoT), 5G, and industry 4.0, this immense influx of data, often left unexamined, poses both challenges and opportunities.

If we could rise to the challenge of processing at least the bulk of the data flood, we can unleash many momentous societal benefits. I would encourage the next generation of computer architects to move to data-centric architectures and leave behind compute-centric designs. There are several compelling paradigms, including in-memory computing and domain-specific customization, that can be leveraged to accomplish this.

### What are some of the main challenges for in-memory computing?

The key problem in realizing 'practical' in-memory computing is building a software ecosystem. This is not a unique problem: graphics processing units (GPUs) faced and overcame it by building CUDA programming frameworks and a customized system-software stack. For in-memory computing there are several programming models, and our community needs to converge.

Another challenge is data staging, i.e. the problem of placing and aligning data. Von Neumann architectures simply solve this problem by moving data from any memory location to registers via loads, and compute units work out of registers. In-memory computing is unique since the memory units are themselves compute units, thus operand data must be placed

in the correct memory locations and moved around minimally between computing.

On the technology side, exciting opportunities exist in architecting emerging memory devices such as ferroelectric memories, magnetic memories, and new genres of resistive memories.

### How is your research applied?

Our prior work repurposes thousands of existing cache memory arrays into massive vector compute units, providing parallelism several orders of magnitude higher than a contemporary GPU. Additionally, it saves energy spent shuffling data between storage and compute units - a significant concern in big-data applications. Caches that compute can be a game changer for AI: they can add accelerator capabilities to general-purpose processors, avoiding the significant die-area cost of a dedicated accelerator. For example, we showed that compute-enabled caches in Intel Xeon can improve processor efficiency by 629x for convolutional neural networks (CNNs).

Our research also extends into precision health and genome sequencing, with certain projects requiring a meticulous co-design approach, incorporating wet-lab procedures, computational biology algorithms, and hardware design. The significance of genetic molecular markers cannot be overstated, particularly for surgical decision-making, cancer diagnosis, and clinical trial enrolment. One notable accomplishment of our research is the demonstration of ultrarapid sequencing of brain-tumour tissue in under 40 minutes; typically, this takes several days to weeks for a lab sendout. Our breakthrough has promising implications for advancing surgical procedures for tumour removal and diagnosis.

HiPEAC 2024 keynote speaker Mitsuhisa Sato has been a deputy director of RIKEN Center for Computational Science since 2018, and is the research team leader of the programming environment research team at the RIKEN Center for Computational Science (R-CCS). He was involved in the project to develop the flagship Japanese supercomputer, Fugaku, which held the number one spot on the Top500 list of the world's most powerful computers from June 2020 until November 2021, and which was number 4 at the time of writing. HiPEAC asked Professor Sato about his work at RIKEN, choosing a supercomputer architecture, and why we need more computing power.

# 'The effective use of silicon is becoming more important'

### Could you tell us a bit about your career so far?

I worked for Real World Computing Partnership, Japan, from 1996 to 2001 as the head of the parallel and distributed system performance laboratory. In this project, I was leading computercluster technology and the Omni OpenMP compiler project. I worked as director of the Center for Computational Sciences at the University of Tsukuba from 2007 to 2013, leading the development of supercomputers using computer-cluster technology.

In 2010, I joined RIKEN as the research team leader of the programming environment research team at the RIKEN Center for Computational Science (R-CCS). From 2014 to 2020, I was working as a team leader of architecture development team in the FLAGSHIP 2020 project to develop the flagship Japanese supercomputer, Fugaku. Since 2023, I have been working as division director of the Quantum HPC Hybrid Computing Platform Division at R-CCS.

### Why was an Arm-based architecture chosen for Fugaku?

Our vender partner was Fujitsu. They used the SPARC instruction set architecture (ISA) for the K supercomputer, the predecessor to Fugaku, but it is now obsolete. At the beginning of the development of Fugaku, the choice of ISA was Intel or Arm. Although Arm was mainly used for embedded processors at that time, we made the decision to use Arm since the company was

interested in the market of high-performance computing (HPC) and high-end servers. Fujitsu contributed to the design of the SVE (Scalable Vector Extension) instruction set for HPC.

Supercomputers are already so powerful - why do we constantly need more computing power? Which research directions (e.g. quantum) do you think will get us there in the face of a slowing Moore's Law?

New application areas such as artificial intelligence (AI) are emerging. New information technology (IT) infrastructure – such as cyber-physical systems (CPS) and digital twins - demands more computing power. Although the progress of silicon technology is slowing, the effective use of silicon is becoming more important thanks to novel architectures such as applicationspecific accelerators.

Quantum computing cannot be a general solution because its applications areas are limited. But it will be revolutionary, and it will lead to ground-breaking breakthroughs in some applications.

### What about making supercomputers more efficient?

Looking at several supercomputer centres, the power capacity limit seems about 50MW from an economic standpoint. The capacity will gradually increase, but the computational demands will increase more rapidly, so it is important to improve efficiency.

Fugaku broke new ground in HPC thanks to its Arm-based architecture

Combining technologies from the web, cyber-physical systems (CPS), the cloud, the internet of things (IoT), digital twins, and AI into a coherent, federated ecosystem, the "next computing paradigm" is the main focus of the HiPEAC Vision 2024. In this article the HiPEAC Vision editorial board picks out the highlights.

# Making the "next computing paradigm" a reality: The HiPEAC Vision 2024

For some years now, it has been obvious that technology is evolving faster than humans can adapt - witness, for example, the dizzying progress of artificial intelligence (AI) - while, at the same time, geopolitical and environmental pressures, such as global warming, are intensifying. Given this context, it is important that the European ecosystem of computing systems reacts quickly and efficiently to improve its place within the competition and proposes solutions that conform to 'European' ethics.

This HiPEAC Vision 2024 sets out our vision of how Europe could do this: through the 'next computing paradigm' (NCP), a convergence of key technologies from the web, cyber-physical systems (CPS), the cloud, the internet of things (IoT), digital twins, and AI into a coherent, federated ecosystem. This ecosystem emphasizes spatial computing, (generative) AI at the edge, dynamic web integration, user-centric models and intelligent, efficient and trustable orchestration of distributed services. Europe should work on building a coherent NCP and promote it as a worldwide approach.

Although based on existing technologies, the NCP will be highly disruptive. As the main highlight of the HiPEAC Vision 2024, it will rely on a synergy of the results of recommendations in the other topics outlined in the document.

### Recommendations of the HiPEAC Vision 2024

As the HiPEAC Vision is now updated every year, many of the recommendations of the previous HiPEAC Vision necessarily still hold, and the same principle of 'leadership races' - in artificial intelligence, hardware, cybersecurity, and sustainability - is still used to structure them. However, this edition focuses on how these elements will contribute to and shape the NCP.

Promote the next computing paradigm and develop the technologies that will make it happen

- Develop 4D-aware implementation technologies, standardizing representation and protocols for encoding physical objects and spaces, supporting mobile computation, and powering 4D-enabled operations.

- · Augment APIs for interoperability, enhancing APIs with specifications for non-functional properties and dynamic service composition.

- Enable the mobility of computation, relocating data and processes as needed

- · Adopt (generative) Al at the edge for greater efficiency and privacy, and reduced latency.

- Develop AI-powered edge orchestrators that can dynamically combine services based on user needs.

- Encourage non-proprietary integration by supporting open standards and platforms.

- Initiate proof-of-concept efforts, creating demonstrators to showcase the advantages of NCP technologies.

Make the EU a strong player in artificial intelligence, particularly for widespread use at the edge

- Support EU growth in AI domains by investing in AI research and infrastructure.

- · Develop foundation models based on 'European values' and reflecting regional needs.

- Promote open-source AI models to enable access to shared AI resources.

- Develop local AI solutions and specialized accelerators for edge devices

- Use AI for software and hardware development, upskilling engineers and researchers.

- · Develop policies around AI accessibility and societal impact, ensuring equitable benefits from AI.

- Ensure 'correctness by construction', automating Al output verification for trustworthiness.

### Develop innovative and efficient new hardware solutions, from architecture to technology

- · Continue to improve performance and energy efficiency, including by exploring and integrating new technologies.

- Promote interdisciplinary research, driving new hardware paradigms.

- Explore innovative architectures for data-intensive computing.

- Develop a full European ecosystem, promoting fast prototyping and specialized architectures and developing the chiplet / interposer European ecosystem.

- Ensure sustainable hardware development, focusing on energy and emission reduction, and recyclability.

### Make cybersecurity a major upfront concern in every computing system

- Address vulnerabilities, building systems with early consideration of cybersecurity and privacy.

- Reduce dependence on external ICT, using trusted European companies or open-source solutions instead.

- Address security challenges in large language models (LLMs).

### Make sustainability lifecycle assessment a requirement for all new computing systems

- Create validated lifecycle models that model environmental impact.

- Develop sustainability-focused design, accounting for environmental costs in product design.

- Create viable sustainable business models for the ICT industry.

- Create ICT solutions for green applications in other industrial sectors.

### In all domains, foster global thinking and promote cross-domain / cross-topic collaborations

- Promote collaboration: encourage teamwork across European research and technology groups.

- Cross-domain project calls: foster interdisciplinary research for innovative solutions.

- Competence centres: create centralized European expertise hubs.

- Build open-source ecosystems to accelerate innovation and accessibility.

- Multi-dimensional tooling: develop tools supporting capacity to address complex and critical challenges.

- · Adopt a holistic approach to efficiency, emphasizing global co-design and system thinking.

It has become increasingly obvious that digital technology in general, and the web in particular, constitute critical infrastructure, and that control over these technologies has major implications for geopolitics. Given the cross-cutting importance of technological autonomy for the EU, the topic of sovereignty is now more focused and is included in each key area.

### FURTHER READING

For this edition of the HiPEAC Vision, the main recommendations are in one document, while a second document, titled 'Rationale', brings together the supporting material. In addition to the main recommendations, we encourage readers to look at the more detailed 'Rationale' document, which is structured according to the main themes of the HiPEAC Vision 2024, helping readers understand the current situation, the forecast of things to come, and the reasons why this set of recommendations was formulated.

If you would like a print copy of the 'Rationale' document, please contact us: A info@hipeac.net

### ✓ vision.hipeac.net

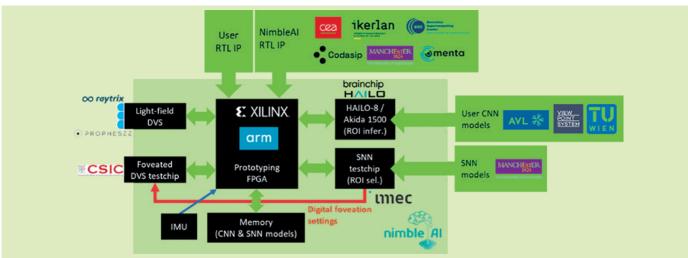

The NimbleAl project, funded by the European Union's Horizon Europe programme, is developing a sensing-processing neuromorphic 3D chip that is inspired by the detection of light in eyes and the processing of visual information in brains. Looking to biological systems for inspiration, the project aims to deliver significant efficiency gains compared to mainstream processors. HiPEAC caught up with NimbleAI coordinator Xabier Iturbe (IKERLAN) to find out more.

# Eye spy NimbleAI's quest for a bio-inspired 3D chip for computer vision

Which biological systems provide inspiration for this project?

We are taking inspiration from both insect and vertebrate visual systems. We are designing a novel foveation mechanism that is, a mechanism to boost resolution in

selected regions or objects - for dynamic vision sensors (DVS). This will allow to dynamically adjust DVS resolution based on the value of visual information each sensor region brings to the application: a visual scene is sensed in low resolution to detect regions of interest to be foveated, that is, sensed in high resolution for better accuracy. The foveation is driven by selective-attention algorithms inspired by central and peripheral vision in vertebrates, which together provide an extremely efficient visual information-gathering mechanism.

We have also built the first-ever light-field DVS that captures directional information of incoming light to enable event-driven, ultra-low-latency and energy-efficient depth perception. This is

inspired by the structure of compound insect eyes, which allow for effective depth and motion detection using very simple neural networks in the insects' tiny brains. To some extent, NimbleAI's neuromorphic vision is inspired by the sort of foveated compound eyes in dragonflies and mantises, which allow them to combine high-resolution vision of their prey with 3D perception to coordinate precise, swift aerial attacks. The NeuroEdge workshop, co-located with HiPEAC 2024, will elaborate on these concepts.

# How do you plan to translate this biological inspiration into

We are adopting a time- and cost-effective approach that relies on reusing and extending the capabilities of existing technology (for example, using Prophesee DVS to capture light-fields). We are producing standalone testchips to implement new capabilities that are not commercially available, especially those related to the novel sensing mechanisms envisioned in the project, such as foveation. In parallel, we will be demonstrating how the different NimbleAI sensing and processing components work together at

The NimbleAI PCB prototype to be delivered in Q4 2024 (some components will be available later)

the logical and physical levels. We are advancing towards an actual 3D physical implementation of key components related to the novel NimbleAI vision modalities: the foveated DVS, lightfield DVS and spiking neural network (SNN) engine that runs selective-attention algorithms. The latter components are to be partitioned and laid across at least three layers in the NimbleAI 3D silicon stack, allowing for the combination of different process technologies with specific support for features like low-noise image pixels and advanced high-performance nodes for neuralnetwork processing. Although the project budget doesn't stretch to manufacturing and assembling such a complicated 3D chip, we will carry out a physical implementation including physical verification and sign-off to ensure technology feasibility.

In parallel, we are building a miniaturized printed circuit board (PCB) prototype that integrates NimbleAI testchips, commercial AI chips and a field-programmable gate array (FPGA), to emulate the functionality of the intended 3D chip. The expectation is that this prototype will help attract early adopters of the NimbleAI technology by allowing user applications to be tested on the emulated NimbleAI chip using live input data captured by NimbleAI DVS sensors and running users' convolutional neural networks (CNNs) on commercial AI chips, or on NimbleAI components prototyped on the FPGA. Both technology feasibility and adoption interest are key to continue developing the NimbleAI concept into an integrated 3D chip, and we expect to fulfil these two requirements within the project timeframe.

### How is NimbleAI progressing in its objectives?

The design of the foveated DVS sensor is almost complete and will soon be sent to the foundry for manufacturing. The lightfield DVS prototype has already been assembled and the first realworld datasets collected in an automotive setting. This allows us to validate the algorithms that we have been designing during the first year of the project using synthetic datasets. Likewise, CEA's computational memory has been optimized to run CNN inference on highly sparse DVS data.

### What results can we expect over the next few months?

Once the light-field DVS algorithm is validated using real-world datasets, we will move from simulation to register transfer level (RTL) design and FPGA prototyping. This will be key to ensuring that the algorithm is not only useful in terms of efficiency and accuracy, but also delivers results with ultra-low latency. In fact, we expect ultra-low latency to be a key advantage of NimbleAI technology as, to the best of our knowledge, there is no passive 3D perception solution in the sub-millisecond range.

By the end of 2024 we will have a clearer view of the performance of our 3D perception algorithm using live real-world data. By the second quarter of 2024, Raytrix will have completed the adaptation of its software development kit (SDK) to support light-

A motorcyclist captured in the first-ever light-field DVS dataset

field DVS data, allowing potential adopters of this technology to experiment with neuromorphic 3D perception. In early 2024, we will also launch the 3D silicon integration activities using the electronic design automation (EDA) tool and sensing and processing components designed in the first half of the project. Finally, the first functional prototype of the NimbleAI 3D chip, including platform software and hardware, will be available by the fourth quarter of 2024. We would encourage anyone wishing to test their vision pipelines on this prototype to contact us, so that they can harness the biological advantage of NimbleAI technology.

### What kind of applications would you see this technology being used for?

Any application that requires energy-efficient and low-latency vision, especially those in which 3D perception is also important. Partner use cases in NimbleAI are good examples:

- automated and autonomous driving by AVL (where the focus is on ultra-low latency to react quickly to unexpected obstacles)

- · eye tracking by Viewpointsystem (which focuses on energy efficiency for use in lightweight glasses)

- portable medical devices by ULMA Medical (where again the focus is on energy efficiency)

Beyond these, we target drone navigation and robotics, as well as space applications. In fact, we are discussing collaborations with the European Space Agency (ESA) and other key stakeholders in the space industry to explore the benefits of NimbleAI technology for space rendezvous and landing manoeuvres. Finally, we are also exploring the use of NimbleAI technology as an enabler for novel AI algorithms which have not yet made their way to industry, including neural circuit policy networks by TU Wien.

The NeuroEdge workshop at HiPEAC 2024 will expand on topics discussed in this article, in particular the talk titled 'I spy with my little insect eyes: Combining DVS and light-fields' neuroedge.eu

NimbleAI has received funding from the EU's Horizon Europe research and innovation programme (grant agreement 101070679), and from UK Research and Innovation (UKRI) under the UK government's Horizon Europe funding guarantee (grant agreement 10039070).